PCI����оƬ

PCIE�����

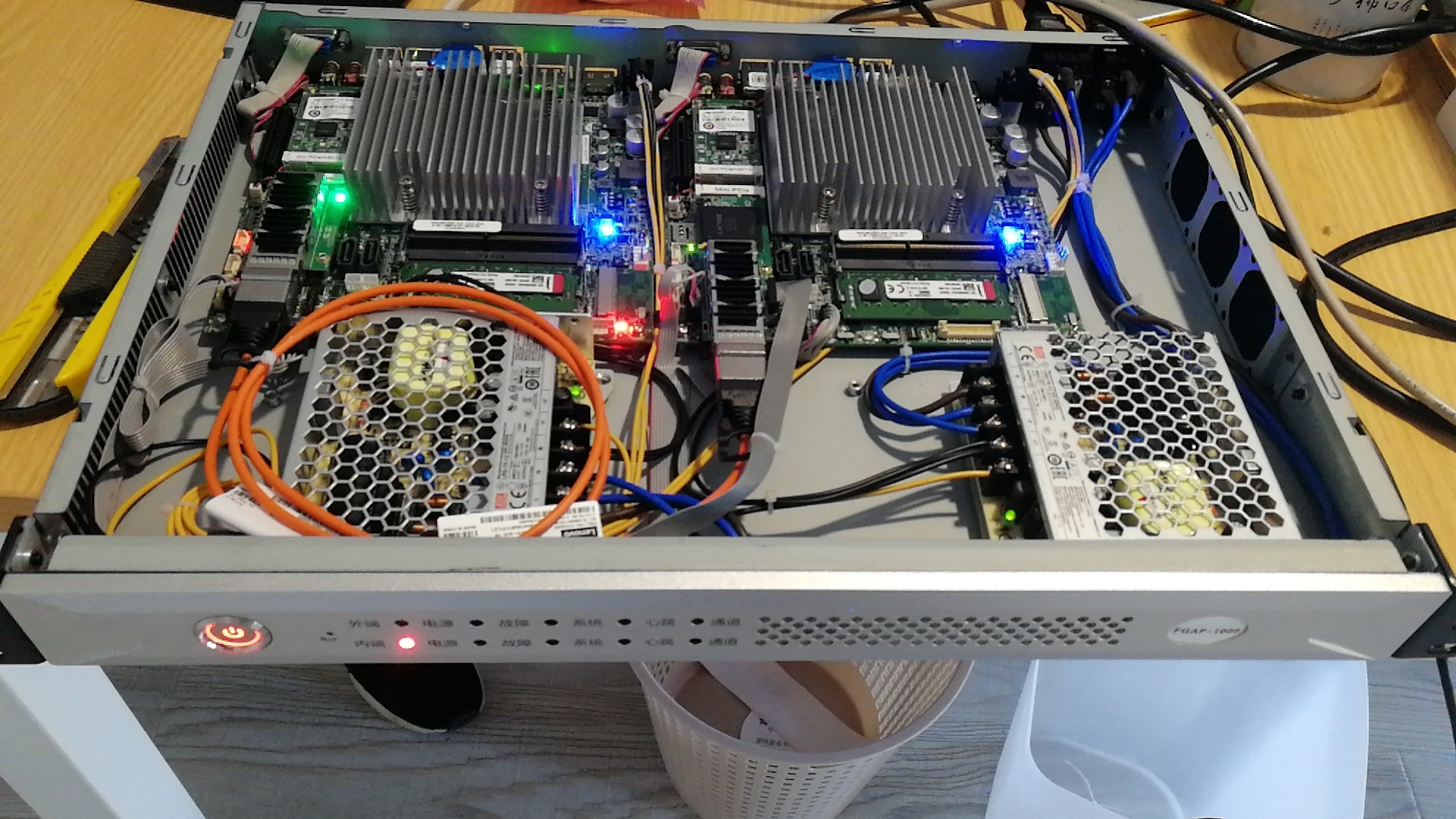

������PCI/PCI-E�ӿڼӽ����оƬ���ǿ�ͨ�õ���������Э����������Ƕ������Ӳ����������ģ�飬��оƬ�ǿ�ͻ

��ģʽʵ�ִ����ݿ�ļӽ������㡣���ڲ�����ͨ�õ�PCI/PCI-E�ľֲ����߽ӿڣ����Է����Ƕ����������ʽ�e�ļ���

��ϵͳ�У���PC�����ʼDZ������ַ������������ϵ����豸�ȡ�

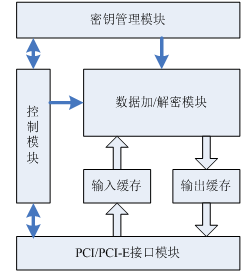

оƬ��ϵ�������ͼ1��ʾ��

ͼ1 оƬ��ϵ�ṹͼ

�ڲ��ߡơ���ģ����Ҫ�ɣ�A)���ݼӽ���ģ�飻B)��Կ����ģ�ѿ飻C)����ģ�飻D)���߽ӿ�ģ����ɡ�

����ͨ���У�

A)����ͨ��PCI/PCI-E�ӿڣ���Ҫ��/���ܦ��������������뻺���У����ݼ�/����ģ���ڿ���ģ��Ŀ�������ɼ�/����

���㣬��������õ����ݨv������������У�PCI/PCI-E�ӿ�ģ�����ս����ݷ��ء赽�����ڴ��У�

B)����ͨ��PCI/PCI-E�ӿ������ģ�鷢��ָ����ƻ����ȡ��ǰ��/���ܡ�ģ�����Կ����ģ���������״̬��

C)��Կ����ģ����оƬ�ⲿUSB�ӿ��ͻ����ܿ�����Կ����Կ�������ϣ�������Կ�Ĺ�������������ݼ�/����ģ��

������Կ�����ɡޡ���֤���洢�ͳ����ȡ�

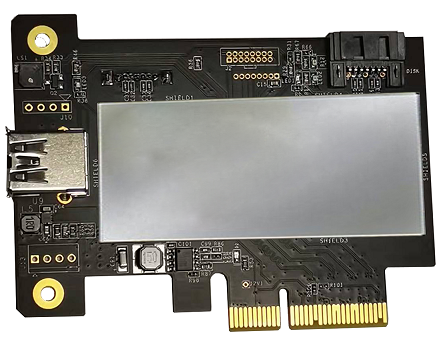

�ص�

2 ���ÿ��ۺϡ��ɸ��õ�Verilog-HDL������ƣ���������ר�ü��ɵ��·��

2 ���õ�ʱ����ͬ��������ƣ�оƬ�Ƴɼ��ɱ��ͣ�

2 PCI���߽ӿ���ѭ�淶2.2���������ݿ���Ϊ32λ��ʱ��Ƶ��Ϊ66MHz�������ܣ��ɹ�������/����ʽ��

2 PCI-E���߽ӿ���ѭ�淶2.0������4X�Ľӿ�ģʽ��

2 Ϊ�˱�֤����֮��ĸ������ݨK���䣬���ô�������˫��ͬ��SRAM��ΪFIFO��

2 ��Ƕ������Ӳ��/��������ģ�飬֧����SM4��DES��TDES��AES�ȶԳƼ����㷨��

2 Ҳ������Ƕ����ң�������Կ�㷨����SM2��RSA��ECC�ȣ�ģ����ب��������㷨��

2 ��Ƕ8051�����������ڶ����ܿ���Կ�Ĺ�����

2 ����PCI ROM����ʵ���èK���������֤��ʵ�ֿ���Ҫ����Կ�Ϳ��

2 ֻ��ͨ���û��������֤�����ܴ��������ܼ�����Կ����������������

2 ����XOR Flash���ƽӿڣ�����ʵ��ROM��λ�ã�

2 ������̨ʽ�������������ʼDZ��͡������ƶ�����ͨ���豸�ȡ�